Advanced Design System 2011.01

Feburary 2011 Allegro Design Flow Integration

## © Agilent Technologies, Inc. 2000-2011

5301 Stevens Creek Blvd., Santa Clara, CA 95052 USA

No part of this documentation may be reproduced in any form or by any means (including electronic storage and retrieval or translation into a foreign language) without prior agreement and written consent from Agilent Technologies, Inc. as governed by United States and international copyright laws.

#### Acknowledgments

Mentor Graphics is a trademark of Mentor Graphics Corporation in the U.S. and other countries. Mentor products and processes are registered trademarks of Mentor Graphics Corporation. \* Calibre is a trademark of Mentor Graphics Corporation in the US and other countries. "Microsoft®, Windows®, MS Windows®, Windows NT®, Windows 2000® and Windows Internet Explorer® are U.S. registered trademarks of Microsoft Corporation. Pentium® is a U.S. registered trademark of Intel Corporation. PostScript® and Acrobat® are trademarks of Adobe Systems Incorporated. UNIX® is a registered trademark of the Open Group. Oracle and Java and registered trademarks of Oracle and/or its affiliates. Other names may be trademarks of their respective owners. SystemC® is a registered trademark of Open SystemC Initiative, Inc. in the United States and other countries and is used with permission. MATLAB® is a U.S. registered trademark of The Math Works, Inc.. HiSIM2 source code, and all copyrights, trade secrets or other intellectual property rights in and to the source code in its entirety, is owned by Hiroshima University and STARC. FLEXIm is a trademark of Globetrotter Software, Incorporated. Layout Boolean Engine by Klaas Holwerda, v1.7 http://www.xs4all.nl/~kholwerd/bool.html . FreeType Project, Copyright (c) 1996-1999 by David Turner, Robert Wilhelm, and Werner Lemberg. QuestAgent search engine (c) 2000-2002, JObjects. Motif is a trademark of the Open Software Foundation. Netscape is a trademark of Netscape Communications Corporation. Netscape Portable Runtime (NSPR), Copyright (c) 1998-2003 The Mozilla Organization. A copy of the Mozilla Public License is at http://www.mozilla.org/MPL/ . FFTW, The Fastest Fourier Transform in the West, Copyright (c) 1997-1999 Massachusetts Institute of Technology. All rights reserved.

The following third-party libraries are used by the NlogN Momentum solver:

"This program includes Metis 4.0, Copyright © 1998, Regents of the University of Minnesota", <u>http://www.cs.umn.edu/~metis</u>, METIS was written by George Karypis (karypis@cs.umn.edu).

Intel@ Math Kernel Library, <a href="http://www.intel.com/software/products/mkl">http://www.intel.com/software/products/mkl</a>

SuperLU\_MT version 2.0 - Copyright © 2003, The Regents of the University of California, through Lawrence Berkeley National Laboratory (subject to receipt of any required approvals from U.S. Dept. of Energy). All rights reserved. SuperLU Disclaimer: THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT OWNER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO, PROCUREMENT OF

SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

7-zip - 7-Zip Copyright: Copyright (C) 1999-2009 Igor Pavlov. Licenses for files are: 7z.dll: GNU LGPL + unRAR restriction, All other files: GNU LGPL. 7-zip License: This library is free software; you can redistribute it and/or modify it under the terms of the GNU Lesser General Public License as published by the Free Software Foundation; either version 2.1 of the License, or (at your option) any later version. This library is distributed in the hope that it will be useful, but WITHOUT ANY WARRANTY; without even the implied warranty of MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the GNU Lesser General Public License for more details. You should have received a copy of the GNU Lesser General Public License along with this library; if not, write to the Free Software Foundation, Inc., 59 Temple Place, Suite 330, Boston, MA 02111-1307 USA. unRAR copyright: The decompression engine for RAR archives was developed using source code of unRAR program. All copyrights to original unRAR code are owned by Alexander Roshal. unRAR License: The unRAR sources cannot be used to re-create the RAR compression algorithm, which is proprietary. Distribution of modified unRAR sources in separate form or as a part of other software is permitted, provided that it is clearly stated in the documentation and source comments that the code may not be used to develop a RAR (WinRAR) compatible archiver. 7-zip Availability: http://www.7-zip.org/

AMD Version 2.2 - AMD Notice: The AMD code was modified. Used by permission. AMD copyright: AMD Version 2.2, Copyright © 2007 by Timothy A. Davis, Patrick R. Amestoy, and Iain S. Duff. All Rights Reserved. AMD License: Your use or distribution of AMD or any modified version of AMD implies that you agree to this License. This library is free software; you can redistribute it and/or modify it under the terms of the GNU Lesser General Public License as published by the Free Software Foundation; either version 2.1 of the License, or (at your option) any later version. This library is distributed in the hope that it will be useful, but WITHOUT ANY WARRANTY; without even the implied warranty of MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the GNU Lesser General Public License for more details. You should have received a copy of the GNU Lesser General Public License along with this library; if not, write to the Free Software Foundation, Inc., 51 Franklin St, Fifth Floor, Boston, MA 02110-1301 USA Permission is hereby granted to use or copy this program under the terms of the GNU LGPL, provided that the Copyright, this License, and the Availability of the original version is retained on all copies. User documentation of any code that uses this code or any modified version of this code must cite the Copyright, this License, the Availability note, and "Used by permission." Permission to modify the code and to distribute modified code is granted, provided the Copyright, this License, and the Availability note are retained, and a notice that the code was modified is included. AMD Availability: http://www.cise.ufl.edu/research/sparse/amd

UMFPACK 5.0.2 - UMFPACK Notice: The UMFPACK code was modified. Used by permission. UMFPACK Copyright: UMFPACK Copyright © 1995-2006 by Timothy A. Davis. All Rights Reserved. UMFPACK License: Your use or distribution of UMFPACK or any modified version of UMFPACK implies that you agree to this License. This library is free software; you can redistribute it and/or modify it under the terms of the GNU Lesser General Public License as published by the Free Software Foundation; either version 2.1 of the License, or (at your option) any later version. This library is distributed in the hope that it will be useful, but WITHOUT ANY WARRANTY; without even the implied warranty of MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the GNU Lesser General Public License for more details. You should have received a copy of the GNU Lesser General Public License along with this library; if not, write to the Free Software Foundation, Inc., 51 Franklin St, Fifth Floor, Boston, MA 02110-1301 USA Permission is hereby granted to use or copy this program under the terms of the GNU LGPL, provided that the Copyright, this License, and the Availability of the original version is retained on all copies. User documentation of any code that uses this code or any modified version of this code must cite the Copyright, this License, the Availability note, and "Used by permission." Permission to modify the code and to distribute modified code is granted, provided the Copyright, this License, and the Availability note are retained, and a notice that the code was modified is included. UMFPACK Availability: http://www.cise.ufl.edu/research/sparse/umfpack UMFPACK (including versions 2.2.1 and earlier, in FORTRAN) is available at http://www.cise.ufl.edu/research/sparse . MA38 is available in the Harwell Subroutine Library. This version of UMFPACK includes a modified form of COLAMD Version 2.0, originally released on Jan. 31, 2000, also available at http://www.cise.ufl.edu/research/sparse . COLAMD V2.0 is also incorporated as a built-in function in MATLAB version 6.1, by The MathWorks, Inc. http://www.mathworks.com . COLAMD V1.0 appears as a column-preordering in SuperLU (SuperLU is available at http://www.netlib.org ). UMFPACK v4.0 is a built-in routine in MATLAB 6.5. UMFPACK v4.3 is a built-in routine in MATLAB 7.1.

Qt Version 4.6.3 - Qt Notice: The Qt code was modified. Used by permission. Qt copyright: Qt Version 4.6.3, Copyright (c) 2010 by Nokia Corporation. All Rights Reserved. Qt License: Your use or distribution of Qt or any modified version of Qt implies that you agree to this License. This library is free software; you can redistribute it and/or modify it under the

terms of the GNU Lesser General Public License as published by the Free Software Foundation; either version 2.1 of the License, or (at your option) any later version. This library is distributed in the hope that it will be useful,

but WITHOUT ANY WARRANTY; without even the implied warranty of MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the GNU Lesser General Public License for more details. You should have received a copy of the GNU Lesser General Public License along with this library; if not, write to the Free Software Foundation, Inc., 51 Franklin St, Fifth Floor, Boston, MA 02110-1301 USA Permission is hereby granted to use or copy this program under the terms of the GNU LGPL, provided that the Copyright, this License, and the Availability of the original version is retained on all copies.User

documentation of any code that uses this code or any modified version of this code must cite the Copyright, this License, the Availability note, and "Used by permission."

Permission to modify the code and to distribute modified code is granted, provided the Copyright, this License, and the Availability note are retained, and a notice that the code was modified is included. Qt Availability: <u>http://www.qtsoftware.com/downloads</u> Patches Applied to Qt can be found in the installation at:

\$HPEESOF\_DIR/prod/licenses/thirdparty/qt/patches. You may also contact Brian Buchanan at Agilent Inc. at brian\_buchanan@agilent.com for more information.

The HiSIM\_HV source code, and all copyrights, trade secrets or other intellectual property rights in and to the source code, is owned by Hiroshima University and/or STARC.

**Errata** The ADS product may contain references to "HP" or "HPEESOF" such as in file names and directory names. The business entity formerly known as "HP EEsof" is now part of Agilent Technologies and is known as "Agilent EEsof". To avoid broken functionality and to maintain backward compatibility for our customers, we did not change all the names and labels that contain "HP" or "HPEESOF" references.

**Warranty** The material contained in this document is provided "as is", and is subject to being changed, without notice, in future editions. Further, to the maximum extent permitted by applicable law, Agilent disclaims all warranties, either express or implied, with regard to this documentation and any information contained herein, including but not limited to the implied warranties of merchantability and fitness for a particular purpose. Agilent shall not be liable for errors or for incidental or consequential damages in connection with the furnishing, use, or performance of this document or of any information contained herein. Should Agilent and the user have a separate written agreement with warranty terms covering the material in this document that conflict with these terms, the warranty terms in the separate agreement shall control.

**Technology Licenses** The hardware and/or software described in this document are furnished under a license and may be used or copied only in accordance with the terms of such license. Portions of this product include the SystemC software licensed under Open Source terms, which are available for download at <a href="http://systemc.org/">http://systemc.org/</a>. This software is redistributed by Agilent. The Contributors of the SystemC software provide this software "as is" and offer no warranty of any kind, express or implied, including without limitation warranties or conditions or title and non-infringement, and implied warranties or conditions merchantability and fitness for a particular purpose. Contributors shall not be liable for any damages of any kind including without limitation direct, indirect, special, incidental and consequential damages, such as lost profits. Any provisions that differ from this disclaimer are offered by Agilent only.

**Restricted Rights Legend** U.S. Government Restricted Rights. Software and technical data rights granted to the federal government include only those rights customarily provided to end user customers. Agilent provides this customary commercial license in Software and technical data pursuant to FAR 12.211 (Technical Data) and 12.212 (Computer Software) and, for the Department of Defense, DFARS 252.227-7015 (Technical Data - Commercial Items) and DFARS 227.7202-3 (Rights in Commercial Computer Software or Computer Software Documentation).

| About Allegro DFI                                                  | 7  |

|--------------------------------------------------------------------|----|

| Allegro DFI Use Model Overview                                     | 8  |

| What's New in ADS 2011.01                                          | 9  |

| Allegro Platform Overview                                          | 10 |

| Exporting Design Data From Allegro Using Allegro DFI               | 18 |

| Set Up and Configuration for Export To ADS                         | 18 |

| Selecting Net Based Geometry for Export and Placing EM Ports       | 26 |

| Export to ADS                                                      | 53 |

| Saving and Loading States                                          | 57 |

| Importing Allegro DFI Files in ADS                                 | 60 |

| Converting Layers between Strip and Slot Representation            | 69 |

| Creating a Cadence IML file from Simulation Results                | 70 |

| Allegro Tools Hints                                                | 70 |

|                                                                    | 78 |

| Installing Allegro DFI inside Allegro                              | 78 |

| Enabling the Allegro Import Design Kit in ADS                      | 87 |

|                                                                    | 88 |

| Differences between Cadence SiP and Allegro Package Designer (APD) | 91 |

| Export to ADS                                                      | 92 |

|                                                                    | 95 |

# **About Allegro DFI**

The Allegro Design Flow Integration (Allegro DFI) is an add-on to the Cadence Allegro Layout Platform and ADS. This tool is used to export the layout information defined in Allegro into ADS, where you can use the Momentum or FEM simulator to simulate the EM behavior. Using Allegro DFI, you can select specific nets, cross-section layers, and components from a specified area of the layout and then cut them from the design. The cut section of the layout can be saved in the EGS format along with a cross section description of the vertical stack and imported in ADS for EM analysis.

This section introduces the Allegro DFI tool, discusses its benefits, and provides an overview of the process used by Allegro DFI to take selected layout information from a design in Allegro and export it to ADS; where it can be used to run a physical simulation.

#### \rm Note

It is strongly recommended that you carefully use the items of the Export to ADS menu, which is added to Allegro by the Allegro DFI tool. Go through each of them step by step before you export. You should be careful while selecting the portion of the layout that you need for EM analysis (critical nets and a cookie cut of the adjacent power and ground metal). Brute force, complete layout transfer from Allegro to ADS may cause speed, capacity, and performance issues.

## **Supported Software Versions**

Agilent provides Allegro DFI support for the Cadence Allegro SPB platform with the following software versions:

- Versions 15.7, 16.01, 16.2, and 16.3

- Allegro DFI skill code version 4.1.0

- Tools: PCB Editor, Package Designer (APD), Cadence SiP

#### 🖯 Note

Allegro DFI supports Cadence Allegro PCB version 15.7 and higher. Allegro Package Designer and Cadence SiP are supported for versions 16.01 and higher.

The ADS 2011.01 supported version of the Allegro Import Design Kit is version 3.0. Earlier versions will not work with ADS 2011.01 and cannot be converted to work with ADS 2011.01. Version 3.0 of the Allegro Import Design Kit remains compatible with ADS 2009 Update1 but with import support limited to the Allegro Import Design Kit version 2.7 behavior.

Standalone configurations of the Allegro DFI inside the Allegro Platform require access to a Python installation (<u>http://www.python.org</u>). Supported Python versions are 2.5 and 2.6.

Updates in response to problems caused by Cadence ISR updates are provided under the <u>Technical Support Documents and Examples</u> in the section <u>Allegro Design Flow Integration</u>

## **Supported Operating Systems**

See ADS installation guide for supported operating systems for the ADS components of the Allegro DFI.

For information about the supported operating systems for Allegro, refer to Cadence Allegro documentation or the Cadence website at:

http://www.cadence.com

## **Accessing Allegro DFI Documentation**

You cannot access the Allegro DFI documentation from the Allegro PCB editor. To access Allegro DFI documentation you must either:

Open ADS, then from any ADS window select **Help** > **Topics and Index** > **I/O** > **Design Translation** > **Allegro Design Flow Integration**.

Or

Access the Agilent EEsof EDA website: <u>http://eesof.tm.agilent.com/</u> Select Support & Services > Product Documentation > ADS (Current and Archived doc) > ADS 2011.01.

# **Allegro DFI Use Model Overview**

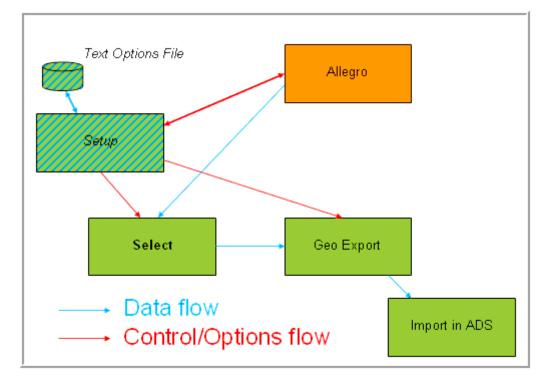

The following diagram depicts the steps for transferring design information from Allegro into ADS:

The internal process flow of the Allegro DFI tool is illustrated in the following figure:

# What's New in ADS 2011.01

ADS 2011.01 supports the following new features in the Allegro DFI:

- Supports Cadence SPB 16.01+

- Enables you to select unnamed electrical objects as RF Ground.

- Supports split ground planes.

- Supports component based selection of pins for port generation.

- Exports selected components in hierarchical design.

- Exports die stacks with bond wires in cdnsipand apd.

- Exports cookie cutter polygon and import of cutter polygon.

- Layers are ordered according to the cross section including drill holes at start of layer list.

- Layers set to 50% transparency.

- Consistent processing of holes in positive and negative shapes.

- Conversion between strips and slots in ADS.

# **Allegro Platform Overview**

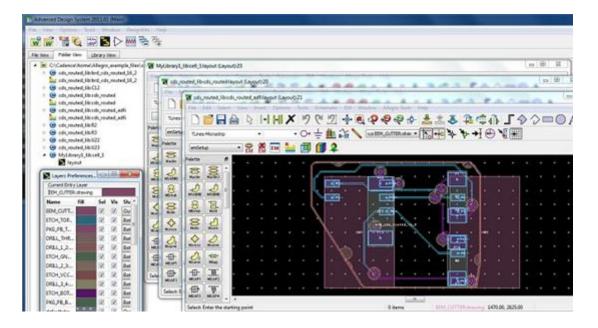

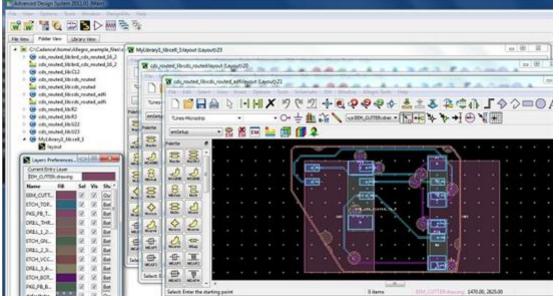

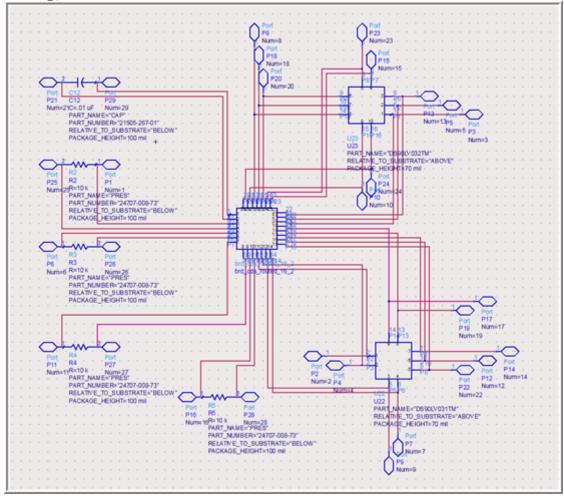

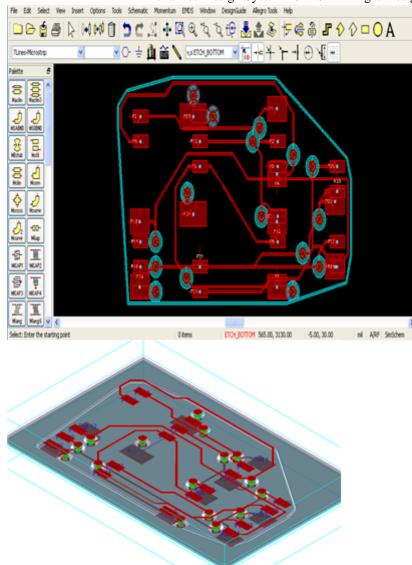

Before using Allegro DFI for transferring design data to ADS, you need to setup a board, package, or module design and create at least a partial layout design in the Allegro Layout platform. The details of designing with the Allegro platform are outside the scope of this documentation, but all users of the Allegro DFI functionality need some basic knowledge about using the Allegro Layout Platform to complete transfer tasks.

This section provides information about basic Allegro features, such as design parameters, cross-sections, classes, options, and edit functions that you need to use inside Allegro during a transfer of your Allegro Layout to ADS with the Allegro DFI.

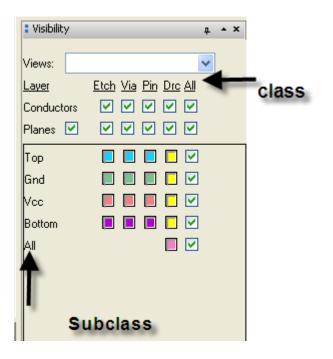

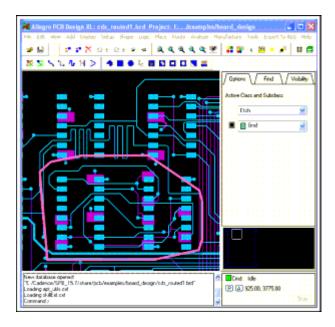

## **Viewing Objects**

In Allegro, database objects are usually organized in a class or subclass hierarchy. You can select the required view for showing classes and subclasses from the **Views** drop-down list. You can also deactivate the class and subclass hierarchy in Allegro. Classes and subclasses used in a cross-section are displayed, as shown in the following figure:

You can also view information about the current active operation in Allegro, as shown in the following figure:

| : Optio | ns                    | ф. | • X |

|---------|-----------------------|----|-----|

| Active  | e Class and Subclass: |    |     |

|         | Etch                  | *  |     |

|         | 🔲 Gnd                 | ~  |     |

|         |                       |    |     |

## **Selecting Objects**

For selecting objects, Allegro uses the following operational model:

- 1. Choose an operation.

- 2. Select an object.

- 3. Apply the operation, choose the next object, or reject the operation.

- 4. Click **Done**.

The application mode may change depending on the command context. You can use the general edit options by right-clicking outside the design. To apply filters, use the **Find** dialog box. While choosing an action, the filter settings used in the last operation are automatically loaded.

| : Find           | <b>д ▲ ×</b>              |  |  |  |  |  |  |  |

|------------------|---------------------------|--|--|--|--|--|--|--|

| CDesign Object F | Design Object Find Filter |  |  |  |  |  |  |  |

| All On All       | Off                       |  |  |  |  |  |  |  |

| Groups           | 🗹 Shapes                  |  |  |  |  |  |  |  |

| Comps            | Voids                     |  |  |  |  |  |  |  |

| Symbols          | 🗹 Cline Segs              |  |  |  |  |  |  |  |

| - Functions      | 🗹 Other Segs              |  |  |  |  |  |  |  |

| 🗹 Nets           | 🗹 Figures                 |  |  |  |  |  |  |  |

| 🗹 Pins           | DRC errors                |  |  |  |  |  |  |  |

| 🗹 Vias           | 🗹 Text                    |  |  |  |  |  |  |  |

| Clines           | ✓ Ratsnests               |  |  |  |  |  |  |  |

| 🗹 Lines          | 🗹 Rat Ts                  |  |  |  |  |  |  |  |

| Find By Name     |                           |  |  |  |  |  |  |  |

| Net              | 🗸 Name 🗸                  |  |  |  |  |  |  |  |

| >                | More                      |  |  |  |  |  |  |  |

|                  |                           |  |  |  |  |  |  |  |

## **Verifying Cross-section Settings**

To specify the cross-section settings, select **Open Setup** > **Cross Section**.

|     | Subclass Name | Туре       |   | Material |   | Thickness<br>(MIL) | Conductivity<br>(mho/cm) | Dielectric<br>Constant | Loss<br>Tangent | Negative<br>Artwork | Shield | Width<br>(MIL) |   |

|-----|---------------|------------|---|----------|---|--------------------|--------------------------|------------------------|-----------------|---------------------|--------|----------------|---|

| 1   |               | SURFACE    |   | AIR      |   |                    |                          | 1                      | 0               |                     |        |                | ^ |

| 2   | TOP           | CONDUCTOR  | • | COPPER   | ٠ | 1.2                | 595900                   | 1                      | 0               |                     |        | 5.00           |   |

| 3   |               | DIELECTRIC | • | FR-4     | ٠ | 8                  | 0                        | 4.5                    | 0.035           |                     |        |                |   |

| - 4 | GND           | PLANE      | • | COPPER   | ٠ | 1.2                | 595900                   | 4.5                    | 0.035           | ×                   |        |                |   |

| 5   |               | DIELECTRIC | • | FR-4     | ٠ | 8                  | 0                        | 4.5                    | 0.035           |                     |        |                |   |

| 6   | VCC           | PLANE      | • | COPPER   | ٠ | 1.2                | 595900                   | 4.5                    | 0.035           |                     |        |                |   |

| 7   |               | DIELECTRIC | • | FR-4     | ٠ | 8                  | 0                        | 4.5                    | 0.035           |                     |        |                |   |

| 8   | BOTTOM        | CONDUCTOR  | • | COPPER   | ٠ | 1.2                | 595900                   | 1                      | 0               |                     |        | 5.00           |   |

| 9   |               | SURFACE    |   | AIR      |   |                    |                          | 1                      | 0               |                     |        |                |   |

In the cross section:

• Negative Artwork is equivalent to Momentum slot mask, but the display shown is

always positive.

- Shield indicates that this is a plane, typically for pwr/gnd distribution. It informs the

router to stay away from it and always exported as sheet conductor by Allegro DFI if

strip export is chosen.

- TOP to BOTTOM defines a physical stack.

- Conducting layers (CONDUCTOR/PLANE) must be separated by dielectric. However, Allegro does not always enforce this rule. If this is not the case, always check the exported substrate stack in ADS because the automatic translation might be inaccurate.

- In traditional Allegro PCB design, only conducting layers get a subclass names. In APD/SiP, dielectric layer can get a name used to define, such as blind or buried vias. The material properties of such layers must be check carefully. The Allegro DFI export does not know the via material in this situation. Always verify the exported cross-section in this case.

## **Defining Padstacks**

To set your preferences for padstacks, choose **Tools > Padstack > Modify Design Padstack** to display the **Options** dialog box, as shown below:

| Coptions                                                                    | μ ▲ ×          |

|-----------------------------------------------------------------------------|----------------|

| Edit<br>O Instance                                                          | e 💿 Definition |

| SMD30_55<br>SMD30_94<br>SMD50_25<br>SMD50_63<br>SMD50_87<br>SMD65REC<br>VIA | 13             |

|                                                                             |                |

| Name:                                                                       | VIA            |

| Symbol:                                                                     | ×              |

| Pin:                                                                        | ×              |

| Refdes:                                                                     | x              |

| New name:                                                                   |                |

| Purge ->                                                                    | Edit Reset     |

Using the Options dialog box:

- You can choose any component in the design, for example a Via in the design.

- You can edit the properties associated with it by clicking **Edit** or right-click **Edit** to open the **Editing Padstack Definition**, as shown below:

| Advanced Design System | em 2011 01 - All | eoro Desion | Flow Integration |

|------------------------|------------------|-------------|------------------|

| Advanced Design Syst   | cm 2011.01 - An  | egio Design | 1 low micgration |

| 🙀 Padstack Designer: I                               | Editing Pad Definition 60C85C35D.pad                                                                                   |                                                              |

|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| Eile Reports Help                                    |                                                                                                                        |                                                              |

| Parameters Layers                                    |                                                                                                                        |                                                              |

| Summary<br>Type: Through                             | Units Mils Decimal places: 2                                                                                           | Multiple drill                                               |

| Etch layers: 4<br>Mask layers: 2<br>Single Mode: Off | Usage options<br>Microvia<br>Allow suppression of unconnected internal pads<br>Enable Antipads as Route Keepouts (ARK) | Rows: 1 Columns: 1<br>Clearance X: 0.00<br>Clearance Y: 0.00 |

| Drill/Slot hole                                      | Top view                                                                                                               |                                                              |

| Hole type:                                           | Circle Drill                                                                                                           |                                                              |

| Plating:                                             | Plated 🗸                                                                                                               |                                                              |

| Drill diameter:                                      | 35.00                                                                                                                  |                                                              |

| Tolerance:                                           | + 0.00 · 0.00                                                                                                          |                                                              |

| Offset X:                                            | 0.00                                                                                                                   |                                                              |

| Offset Y:                                            | 0.00                                                                                                                   |                                                              |

| Non-standard drill:                                  |                                                                                                                        |                                                              |

| Drill/Slot symbol                                    |                                                                                                                        |                                                              |

| Figure:                                              | Circle 🔽                                                                                                               |                                                              |

| Characters:                                          |                                                                                                                        |                                                              |

| Width:                                               | 50.00                                                                                                                  |                                                              |

| Height:                                              | 50.00                                                                                                                  |                                                              |

|                                                      |                                                                                                                        |                                                              |

|                                                      |                                                                                                                        |                                                              |

The **Padstack Designer** dialog box consists of **Parameters** and **Layers** tab. All the information related to component (Via in this case) is displayed in this dialog box. It allows you to suppress unconnected catch pads and plating information (electrical properties), which are specified in the *eemom.option* file.

| 0 | Note                                                              |

|---|-------------------------------------------------------------------|

|   | Multi-drill with staggered holes is not supported in Allegro DFI. |

For setting layers, depending on the nets of the shapes that the via crosses, you can use a Regular pad, Thermal relief pad, or Anti pad.

- Thermal relief is added when a via connects to a plane shape.

- If a plane is all **positive**, relief is created by dynamic routing mechanism.

- If a plane is **negative**, relief shape is inserted in the plane.

| P | arame         | ters Layers       |                |                |              |   |               |

|---|---------------|-------------------|----------------|----------------|--------------|---|---------------|

|   | Pads          | ack layers        |                |                |              |   | Views         |

|   |               | Single layer mode |                |                |              |   | Type: Through |

|   |               | Layer             | Regular Pad    | Thermal Relief | Anti Pad     |   | October O Top |

|   | Bgn           | TOP               | Circle 60.00   | Flash          | Circle 85.00 | ^ |               |

|   | •>            | GND               | Circle 60.00   | Flash          | Circle 85.00 |   |               |

|   | ->            | VCC               | Circle 60.00   | Flash          | Circle 85.00 |   |               |

|   | ->            | DEFAULT INTERNAL  | Circle 60.00   | Flash          | Circle 85.00 |   |               |

|   |               | BOTTOM            | Circle 60.00   | Flash          | Circle 85.00 |   |               |

|   | ->            | SOLDERMASK_TOP    | Circle 75.00   | N/A            | N/A          |   |               |

|   |               | SOLDERMASK_BOTTOM | Circle 75.00   | N/A            | N/A          | ~ |               |

|   |               | <                 |                |                | >            |   |               |

|   |               |                   |                |                |              |   |               |

|   |               | Regular Pad       |                | hermal Relief  |              |   | Anti Pad      |

| G | ieome         |                   |                | Flash          | ~            |   | Circle 🗸      |

|   |               |                   |                |                | -            |   |               |

|   | hape:         |                   |                |                |              |   |               |

| F | lash:         |                   |                | TR_80_60       |              |   |               |

| ٧ | Vidth:        | 60.00             |                | 80.00          |              |   | 85.00         |

| Н | leight        | 60.00             |                | 80.00          |              |   | 85.00         |

|   | )<br>Iffset > | ¢ 0.00            |                | 0.00           |              |   | 0.00          |

|   |               |                   |                |                |              |   |               |

| U | )ffset 'i     | 0.00              |                | 0.00           |              |   | 0.00          |

|   |               |                   |                |                |              |   |               |

|   |               |                   | Current layer: | TOP            |              |   |               |

- Be very cautious with this when you switch between negative/positive in cross section. For example, Thermal relief as circle is working fine on the positive plane, but may disconnect the via when switching to the negative plane.

- The Allegro DFI option allows you to ignore thermal relief on negative layers.

## **Display Parameters**

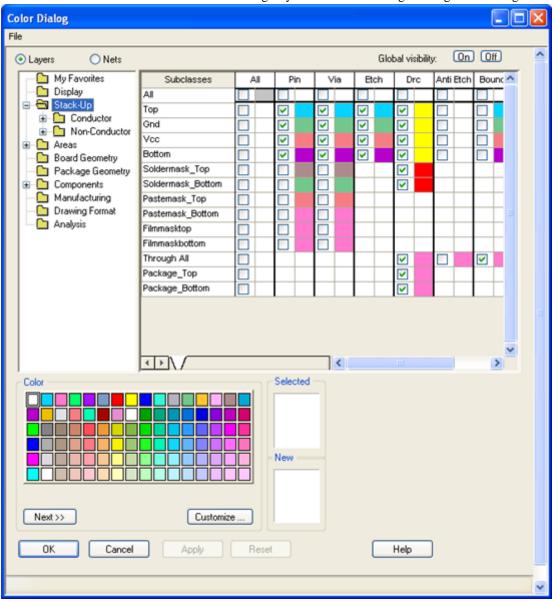

Select **Open Display** > **Color/Visibility** to change the display related parameters. The **Color Dialog** box is displayed, as shown in the following figure:

#### In Color Dialog:

- Allegro DFI uses a scratch layer for cookie cutter, etc. Usually it is called MANUFACTURING/EEM\_SCRATCH. If you get an error message related to the scratch layer, toggle visibility of the Manufacturing layers and click **Apply**. This scratch layer is the only object that is not removed at the end of a Allegro DFI session.

- You can also adjust display bundles, shadow mode, and shapes transparency.

On some graphics cards, OpenGL fails. You need to change the settings by performing the following steps:

- 1. Choose **Setup** > **User Preferences**.

- 2. Choose **Display** > **Opengl**.

- 3. Disable the **opengl** flag and restart Allegro.

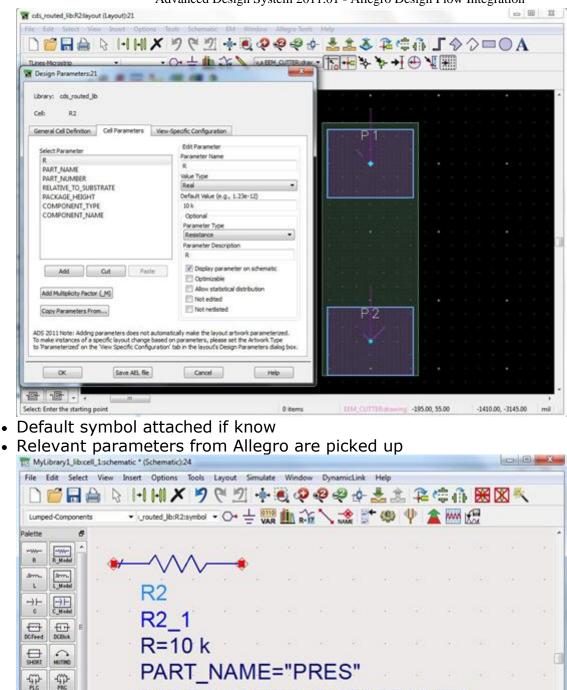

## **Design Parameters**

To set design parameters, choose **Setup** > **Design Parameters**. This displays the Design Parameter Editor, as shown below:

| 🐉 Design Parameter Editor                                                                       |                                                                                                                                |  |  |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Display Design Text Shapes Route Mfg Applications                                               |                                                                                                                                |  |  |  |  |  |  |  |

| Command Parameters                                                                              |                                                                                                                                |  |  |  |  |  |  |  |

| Display                                                                                         | Enhanced Display Modes                                                                                                         |  |  |  |  |  |  |  |

| Connect point size:10.00DRC marker size:100.00Rat T (Virtual pin) size:35.00Max rband count:500 | <ul> <li>Display plated holes</li> <li>Display non-plated holes</li> <li>Display padless holes</li> <li>Filled pads</li> </ul> |  |  |  |  |  |  |  |

| Ratsnest geometry: Jogged V                                                                     | Connect line endcaps                                                                                                           |  |  |  |  |  |  |  |

| Ratsnest points: Closest endpoint 💌                                                             | <ul> <li>Thermal pads</li> <li>Bus rats</li> <li>Waived DRCs</li> <li>Via Labels</li> </ul>                                    |  |  |  |  |  |  |  |

Some of the Design Parameter Editor tabs are described below:

• **Display**: This tab consists of **Display** and **Enhanced Display Modes** sections. It controls how padstacks are displayed. You can set view preferences by selecting the require options. Click **Apply** to implement each option.

| 1 Note                                                          |                              |

|-----------------------------------------------------------------|------------------------------|

| You should note the difference on a board with all positive lay | yers versus negative layers. |

• **Design**: This tab controls the accuracy settings, which corresponds with the ADS layout resolution. The accuracy settings also control substrate export. The following figure displays the Design tab:

| 🚧 Desig | 🎾 Design Parameter Editor                         |                            |                       |  |  |  |  |  |

|---------|---------------------------------------------------|----------------------------|-----------------------|--|--|--|--|--|

| Displa  | y Design Text                                     |                            | oute Mfg Applications |  |  |  |  |  |

|         | User Units:<br>Size:<br>Accuracy:<br>Long Name Si | Mils<br>B<br>2 🗘<br>ze: 31 | (decimal places)      |  |  |  |  |  |

- **Shapes**: You can select the Dynamic and Static Shape options to edit your design in real time or in non-real time.

- Click **Edit global dynamic shape** to check the number of *out of date shapes*.

| 🔀 Design Parameter Editor                                                                                                                                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Display Design Text Shapes Route Mfg Applications                                                                                                                            |

| C Dynamic Shape                                                                                                                                                              |

| Dynamic shapes allow real-time shape updating during interactive etch editing. Shape parameters are<br>structured into a global, shape instance, and object level hierarchy. |

| 🖗 Global Dynamic Shape Parameters                                                                                                                                            |

| Edit global dynar<br>Shape fill Void controls Clearances Thermal relief connects                                                                                             |

| Update to Smooth Out of date shapes: 0/0                                                                                                                                     |

| Dynamic fill: 💿 Smooth 🔿 Rough 🔿 Disabled                                                                                                                                    |

An example of dynamic shape processing is the creation of thermal reliefs and anti-pads on postive shapes.

Operations on big or incomplete designs may disable the dynamic shape update. This can causes incorrect shapes/connectivity and requires manual update before starting an export.

## **Constraint Manager (version 16.x)**

You can define constraints for the following options in a design:

- Spacing, wiring, and delay rules.

- Pad and padstack definitions for blind and/or buried vias and bondfingers.

You do not need an Allegro DFI export for controlling these options. For example, delay constraints for a line can be found in this tool. A tool that checks electrical design rule violations is shown below:

|            |         | hoe Audit Iools Window Heik |        |          |         | (        |           | - (            |          | 1.000    |           | 1000        |          |

|------------|---------|-----------------------------|--------|----------|---------|----------|-----------|----------------|----------|----------|-----------|-------------|----------|

| O K        | 1 0     | 0 2                         | *      | Da 📮     | 6 20    | 1 de 1   | -0.1      | - <del>*</del> | 6+       | Ya       | Y6 🙀      | ¥ %         |          |

| × pe       | chage,  | example_nov2008             |        |          |         |          |           |                |          |          |           |             |          |

|            | Line To |                             |        |          |         |          |           |                |          |          |           |             |          |

| Type       | •       | Objects                     | Line   | Thru Pin | SMD Pin | Test Pin | Thru Via  | 88 Via         | Test Via | Microvia | Shape     | Bond Finger | Hole     |

|            | _       |                             | 1870   | 1000     | 1000    | 1000     | 100       | 1000           | um       | 1000     | um        | um          | um       |

| <u> </u>   | -6-     |                             |        | C        |         |          |           |                |          |          | -         |             |          |

| Dom<br>SCS |         |                             | 79250. |          | 79250   | 79250    | 127.0.25. | 127.0.25       | 127.0.25 | 127-0-25 | 127.0.50. | 127.025.01  | 7.825.0. |

| SCS        | 0       |                             | 1.825  |          | 7.825   | 7.925.   | \$27.AL   | 127.8          | \$27.4   | 127.4    | \$77.AL   |             | 7.825    |

| 505        | 100     |                             | 1.9.70 |          |         |          | 177.4     | 177.8.         | 177.4    | 127.4    | 177.4     |             | 1.5.78   |

|            |         |                             |        |          |         |          |           |                |          |          |           |             |          |

|            |         |                             |        |          |         |          |           |                |          |          |           |             |          |

# **Exporting Design Data From Allegro Using Allegro DFI**

Allegro DFI transfers data targeted at performing an EM simulation. It does not transfer an entire design database. To transfer the entire database you should use other standard mechanisms, like Gerber, stream, IFF, and ODB++ export.

An Allegro DFI export process consists of the following steps:

- 1. Setup

- 2. Selection

- 3. Export

The Allegro DFI export setup and selection is tailored towards gathering the relevant information for setting up and running an EM simulation from ADS. You should be careful while selecting data in Allegro DFI and adjust the export, if necessary. It can save you significant time later when performing the EM simulations in ADS.

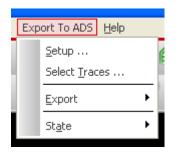

To open Allegro DFI, select **Export to ADS** from the Allegro main menu. This opens the **Export to ADS** drop-down menu, as shown in the following figure:

Selecting **Export > All Artwork** is not the best option as it is an expensive operation, provides no control, and exports flat EGS data and only main substrate. There is little or no other Allegro database information passed, such as no pins, components, or nets.

# **Set Up and Configuration for Export To ADS**

You can configure export by options by selecting **Allegro PCB** > **Export to ADS** > **Setup** to open the **Set Up for Momentum** dialog box. This dialog box is used to select a group of specific configuration options that Allegro DFI needs for exporting files to ADS. You can select an entire group from the drop-down list in this dialog box. The description field is updated according to the chosen selection.

| 👺 Set Up for Momentum Export                                                                                                                                                       | X |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Export Options<br>Export Setting Sample Fine Setting B: use Strips, Slots and Vias                                                                                                 |   |

| Signal viaType asDefined, padType asDefined<br>Ground viaType asDefined, padType asDefined<br>Signal and Ground arcResolution 15 degrees<br>Export negative plane objects as Slots |   |

| Reset/reload All Reload Options OK Cancel                                                                                                                                          | ] |

Using the **Set Up for Momentum** dialog box, you can:

- Determine the way layout primitives are processed during export:

- Behavior with respect to negative objects

- Vias/Padstacks on Signal Nets, or RF ground nets can be treated independently.

- Define layer mapping information.

- Provide default values for the Allegro DFI selection dialog box, e.g. the default port generation options.

You can also use the Set Up for Momentum dialog box for:

- **Resetting or reloading default configuration options**: You may need to restore the default values after an error from Allegro or Allegro DFI environment results an Allegro command or the Allegro DFI into a faulty state. Click the **Reset/Reload All** button to initialize the default configuration of Allegro DFI data structures in the Allegro environment. For example, if you accidentally try to open Allegro DFI before ending an earlier Allegro edit command, you need to restore the default values.

- **Reloading options**: To update an option file, you need to reload the configuration settings. Click the **Reload Options** button to load new or update option configuration files without reloading Allegro.

Allegro DFI provides some predefined example settings setups to allow a quick start with the export tool. In addition, you can easily define customized setups as per your requirements and automatically add them to the selection list in the drop down list.

## **Using the Sample Export Settings**

The Set Up for Momentum dialog box allows you to choose from predefined example settings. These following sample settings consists of a combination of default values with various levels of accuracy for the export process:

- Sample Fine Setting A: use Strips and Vias: This setting consists of the following default values:

- Signal viaType asDefined, padType asDefined

- Ground viaType asDefined, padType asDefined

- Signal and Ground arcResolution 15 degrees

- Converts negative plane objects to strips

- All catch pads are generated

- Sample Fine Setting B: use Strips, Slots and Vias: This setting consists of the following default values:

- Uses Strip/Slot/Via when negative layers present

- Ground viaType asDefined, padType asDefined

- Signal and Ground arcResolution 15 degrees

- Export negative plane objects as Slots

- All catch pads are generated

- Sample Board setting using Strips, Slots and Vias: This setting consists of the the following default values:

- Uses Strip/Slot/Via when negative layers present

- Signal viaType asDefined, padType asDefined

- Ground viaType square, padType asDefined

- Signal and Ground arcResolution 30.0 degrees

- Simplify thermal reliefs on negative shapes

- Remove unconnected catch pads

- Remove holes in RF Ground shapes not overlapping with RF Signal nets

- Use the cutter polygon as board boundary

- Sample Medium Setting: This setting consists of the following default values:

- Signal viaType square, padType square

- Ground viaType square, padType square

- Signal and Ground arcResolution 30 degrees

- Sample Course Setting: This setting consists of the following default values:

- Signal viaType diamond, padType diamond

- Ground viaType diamond, padType diamond

- Signal and Ground arcResolution 45 degrees

- Remove unconnented catch pads

- Simplify thermal via connections

- Remove voids in RF ground shapes that do not overlap signals

#### 🖯 Note

Use *Sample Fine Setting B* for a first time transfer. The transferred design will be similar to the original. However, note that the sample settings may not fit your particular analysis needs. Therefore, you should either modify the default settings and/or add additional custom settings to your site or personal configuration files. You can do this by opening, copying, and modifying the \_eemom.option\_ file(s).

## **Defining Additional Export to ADS Setups**

You can configure the list of settings displayed in the Set Up for Momentum dialog box. This list is created by the concatenation of the contents of *simulation settings* defined in three option files. The title and description fields are selected for display in the setup window and all other values are applied to the internal Allegro DFI configuration fields. The following option files are used:

1. The *\$HPEESOF\_DIR/ial/config/eemom.option* or the file defined by the environment

Advanced Design System 2011.01 - Allegro Design Flow Integration variable *EEMOM\_GLOBALOPTIONSFILE* if this variable exists. This option file describes all the at the end and it can be replaced by an EDA admin by a site specific default option file by defining the *EEMOM\_GLOBALOPTIONSFILE* variable\_.\_

- 2. ~/pcbenv/eemom.option: You can copy the default eemom.option at ~/pcbenv/eemom.option and modify it as per your requirements.

- 3. < Allegro Design Directory >/< designName > .option

- For design specific options, you can also place an option file in the directory of a design, with the base name as the design.

- .eemom

•

in the directory where

.{brd\|mcm\|sip}

is placed.

These files are read in the order given above. In case of duplicate settings in the files,(i.e., settings with the same name), the last setting found will be retained for the final list.

Below we show an example fragment from the default *eemom.option* file used to create the *Export Settings* list. Such a file can be copied and modified according to your specifications with a text editor. The latest version of the default file containing a description of all available configuration settings can always be found in the \$HPEESOF\_DIR/ial/config directory.

#### \rm Note

The content of the files is actually a independent lisp list, (e.g., it has the format (mnemonic [<name>] <definition>))

- *mnemonic* defines what will be defined

- some mnemonics need a name, others do not

- <definition> is a sequence of values or independent lisp lists

If the lisp mnemonic does not have a name the contents of the sections are concatenated. Every file, of this type, must start with *(setupData* and no blank lines, spaces or comment lines are allowed before these tokens. Aside from this, empty files will also generate errors.

```

(setupData

```

```

; mnemonic to mark the start of the setup list

(scratchLayerName "MANUFACTURING/EEM_SCRATCH")

; name of a class/subclass in the allegro board that can be

; used as a scratch layer for the ADS integration for e.g.

; storing the cutter shape ... should not belong to the edge

; class

(egsArcResolution 22.5)

; arc faceting angle used when translating Allegro arcs

; into the output EGS file

; float: (0 < deg < 90) arc resolution used for export

; only for arcs not dealt with in signal or ground

; refacetting step

; nil: use 22.5 degrees

(egsExportResolution 1000)

; int: > 0 preferably a multiple of 10

```

```

Advanced Design System 2011.01 - Allegro Design Flow Integration

; if not specified, the allegro native resolution will be used

(skipGlobalHandling "FALSE")

; determines the strategy to use when preparing the selected

; objects for export to EGS

; skipGlobalHandling does not have any effect for negative

; masks when negativeMasksToStrip "TRUE" as this option

; requires global handling

; flag: true perform boolean operations locally

false perform boolean operations globally

. . .

(gndOpt

(viaType "asDefined")

; determines how the viashapes will be translated in the output

; shape

; string enum: "asDefined"

"square"

"diamond" (i.e., square rotated by 45 deg)

(padType "asDefined")

; determines how the pin and via pads will be translated in the

; output shape

; string enum: "asDefined"

"square"

;

"diamond" (i.e., square rotated by 45 deg)

:

(arcResolution 15.0)

; arc facetting angle used when translating Allegro arcs

; into the output EGS file

; float: (0 < deg < 90) arc resolution used for export

(<= 0) do not refacet arc

; nil: use 22.5 degrees

(minEdgeLength 0.000)

; minimum edge length of segments written into the output EGS

; file (smaller segments are combined until the threshold is

; reached

; float: (>= 0) min edge length in the egs file

; nil: use 0.999999 the layout resolution

; if arcResolution <= 0, this setting is ignored

(viaTfAreaRatio 1.0)

; multiplication factor for vias when translating the original

; shape into the new one. Currently this factor will only

; work correctly for circles to square or diamond

0.000000000000000 delete shape

;

0.7978845608028653 e.g. circle -> inner square

;

0.8862269254527580 same perimeter (if circle->square)

:

1.000000000000000 same area

1.1283791670955125 e.g. circle -> circumvent square

:

(padTfAreaRatio 1.0)

; same behavior as viaTfAreaRatio but for pads instead of vias

(simplifyThermal "TRUE")

; on negative layers only, for the connections to shape structures

; planes

TRUE

: do not generate thermal relief pad polygons

;

FALSE : generate thermal relief pad polygons

;

(sigOpt

; same options as in the gnd opt subsection but now for shapes

; being defined as signal traces

(viaType "asDefined")

(padType "asDefined")

(arcResolution 15.0)

(viaTfAreaRatio 1.0)

```

```

Advanced Design System 2011.01 - Allegro Design Flow Integration

(padTfAreaRatio 1.0)

)

)

); end of setting "Sample Setting A"

)

```

#### 🖯 Note

At least one fully specified option file must exist, else Allegro DFI will not work. After making modifications in an eemom.option file, click **Reload Options** to update the settings list.

## **Using The Option File Sections**

Each option file is a lisp "list expression" stored inside a file. It consists of the following features:

- Must start with "(setupData" and end with ")".

- Uses the Skill syntax for a hierarchical list of (name value(s))

- At least one of the option files must start with the general preferences (requires restart of Allegro to update)

- (scratchLayerName "MANUFACTURING/EEM\_SCRATCH"): cutter layer

- (cutterExpansion 5.0): initial cutter oversize distance

- (firstEgsLayerNum 1001): first layer number used on ADS side

- The export options have the form (simulationSettings(setting ...))

The following options are used in the Option file:

- DrillProps

- Simulation Settings

## **Configuring DrillProps Section**

The DrillProps section allows you to specify the conductivity and other properties of the plating materials for via structures. This is necessary because Allegro is missing this data in the platform UI. In this section:

- Drill -1: Specifies the properties for the DRILL\_THROUGH via

- Drill -2: Specifies the properties used by DRILL\_<i1i2>, the inter-layer vias and some via structure created in named dielectric layers of a cross-section.

```

(drillProps

(drillUnits

(layerThicknessUnits "mil")

(electricalConductivityUnits "mho/cm")

)

(drill -1

(layerType DRILL)

(layerType DRILL)

(layerName "default")

(layerMaterial "COPPER")

(layerThickness 1.0)

(layerElectricalConductivity 595900.0)

)

```

```

(drill -2

(layerType DRILL)

(layerName "other")

(layerMaterial "COPPER")

(layerThickness 1.0)

(layerElectricalConductivity 595900.0)

)

) ; end of drillProps

```

## **Configuring Simulation Settings**

Each block of simulation settings option contains:

- a title used for the drop down list in the setup dialog

- a multi line description field that provided a textual description of this set of settings

- the actual options section with a global list of settings, followed by gnd and/or signal specific settings.

```

(simulationSettings

; start of list of settings available to choose from in the

; setup window

(setting "Sample Setting A"

; name that is displayed in setup dialog drop-down combo box

(description "This Description is viewable in setup dialog"

"This will be displayed as the second line"

"And this is the third line"

"Do not use special escape characters as \n \t")

; description displayed in the setup dialog, 1 string/line

(options ...

```

#### **Frequently used Global Settings**

Some frequently enabled or modified global settings in a simulation option section are described below:

The negativeMasksToStrip setting defines if objects on a negative Allegro layer are exported as strip or slot mask objects for ADS. Convert slot objects into strips objects, if set to "TRUE".

```

(negativeMasksToStrip "FALSE")

; determines how to handle negative masks

; flag: false - negative masks -> slots

; true - negative masks -> strips

```

The gndHoleDropDistance and cutterDefinesCrossingGndHoles settings are useful for strip designs with many complex voids. It allows you to drastically simplify plane like structures with many shapes far away from traces of interest before export.

(gndHoleDropDistance 0.0)

; determines how to handle voids in the RF ground shapes

; depending on their distance to Signal net features they can be

; skipped from export in the egs file

#### Advanced Design System 2011.01 - Allegro Design Flow Integration ; float: (>=0.0) voids further away are dropped form the egs export ; nil or (< 0.0): keep all holes (cutterDefinesCrossingGndHoles "TRUE") ; determines how holes/voids in RF ground shapes are threated ; either as voids with respect to the shape of the board or as ; voids ; with respect to the cutter shape. ; flag: false: only real holes in the original shape are considered for hole removal true: the cutter shape is used to define potential holes in a shape for removal ; Note: when true the cutter outline is followed outside the board outline because this area is essentially also a void region ; with respect to the cutter. ; If board shape must be maintained use either the false setting which is less aggressive or modify the cutter shape to stay within the board boundary.

- The noContourSlotOnNegative settings controls the layer behavior on split ground plane structures on negative planes in Allegro. In this setting:

- ٠

- A contour slot is created by default on negative layers exported as **SLOT** to separate split ground structures. This introduces an non-existent split/discontinuity in the ground plane structure that can disturb the EM simulations.

- When this option is set to **TRUE**, it asks the exporter to skip the generation of this contour slot during the export.

- Avoids editing the slot structure on the ADS side, but shorts split plane structures together on a perfect conducting plane.

- If the split plane structure must be used, specify the following value: (negativeMasksToStrip TRUE)

(noContourSlotOnNegative "FALSE")

```

;determine how to handle shapes on negative masks exported as slot

```

; flag: false - negative masks -> slots with contour slot

true -negative masks -> slots no contour slot

```

negative masks exported as strip donot have contour around the shapes anyhow

```

• You should carefully use the egsMinEdgeLength, autoPortForAllNetPads, and gndHoleDropDistance options.

```

Note

Never change the settings for these options, unless given as a workaround by EEsof support.

```

```

(egsMinEdgeLength 0.000)

; minimum edge length of segments written into the output EGS

; file (smaller segments are combined until the threshold is

; reached

; float: (>= 0) min edge length in the egs file

; nil: use 0.999999 times the layout resolution

(autoPortForAllNetPads "FALSE")

; determine if the automatic port insertion feature will generate individual

```

```

(gndHoleDropDistance <positive float>)

; determines how to handle voids in the RF ground shapes

; depending on their distance to Signal net features they can be

; skipped from export in the egs file

; float: (>=0.0) voids further away are dropped form the egs export

; nil or (< 0.0): keep all holes</pre>

```

#### Frequently used gnd/signal specific settings

The following options are used frequently:

- padType: It is recommended to specify "asDefined", which is handled by Layout simplification.

- viaType: This setting is useful if exact via model is not needed (e.g. for gndvias).

- pathType: It is recommended to specify "rounded", which is handled by Layout simplification.

📵 Tip

Use "mitered" when you have problems with missing segments or flipped arcs on traces. (clines)

• If you get **Allow suppression of unconnected catch pads** error due to incorrect pad stack definition, You can specify the following option:

```

(exportPads "connected")

; string property describing which "catch" pads

; will be generated in the egs output for pins and vias

; "all" : (default) generate all regular pads in the output

; "none : no pads are generate except the ones on outer

; layers

; "connected" : only if a regular connection other than a via exists

; "startend-connect" : "connected setting" + the top and bottom pads

)

```

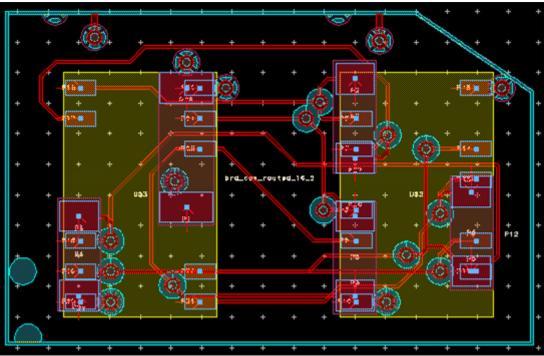

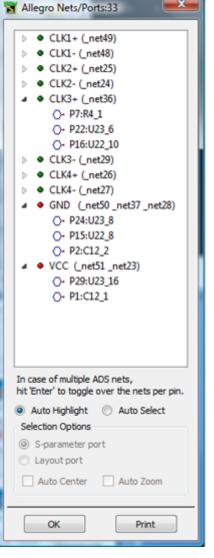

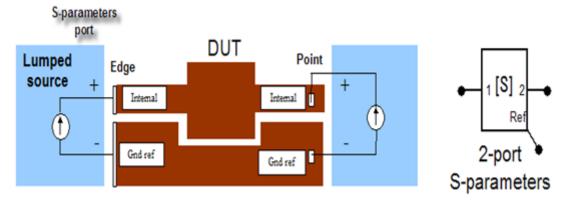

# Selecting Net Based Geometry for Export and Placing EM Ports

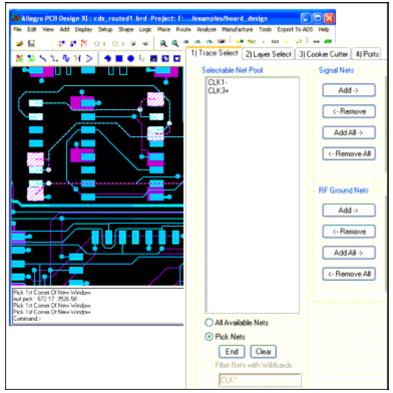

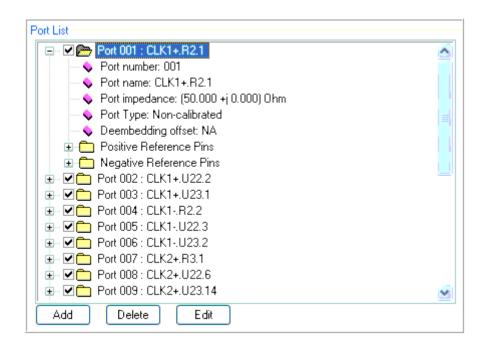

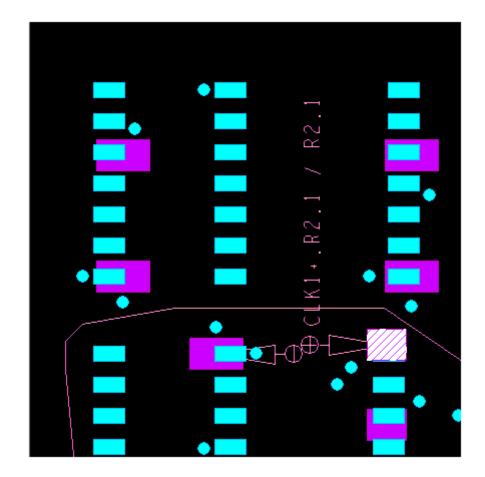

Choose **Export to ADS** > **Select Traces** to open the *Select Geometry and Place Ports* dialog box. This dialog box enables you to choose specific nets and add them to *Signal* and *Ground* output lists for export into ADS, by using the *Trace Select* and *Layer Select* tabs.

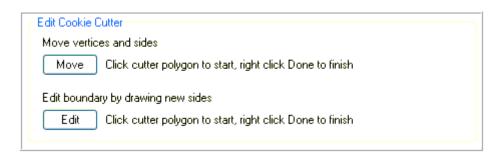

It also enables you to reduce the geometry of the ground nets by using the functions available in the *Cookie Cutter* tab to define a "cutout" shape. Using the cookie cutter, you can reduce the stack of the board, select which layers will be exported and create port definitions for export into ADS.

🖯 Note

By default the cookie cutter feature only acts on ground nets and does not alter the shape of the signal nets.

With the Component/Pin Select you can choose the component pins that are of interest for

the simulation port generation. The *Port* tab enables you to automatically create ports from the selected trace pads, or clear and edit already existing port definitions.

A visual status check is also provided to alert you that a step is complete and ready for export (green), or that more information is required (yellow).

| 🔀 Select Geometry and Place Ports                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                              |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1) Trace Select 2) Laver Select 3) Co                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | pokie Cutter 4) Component/Pin Select 5) Ports                                                                                |  |  |  |  |

| Selectable Net Pool           A1           A2           A3           A4           A5           A6           A7           A8           A9           A10           A11           A12           A3           A4           A5           A6           A7           A8           A9           A10           A11           A12           A13           A14           A15           A16           A17           A18           A19           A20           A21           A22           A23           ADDR0           ADDR1 | Signal Nets   Add ->   Add All ->   Add All -> <b>RF Ground Nets</b> (- Remove Add All -> (- Remove Add All -> (- Remove All |  |  |  |  |

| All Available Nets     All Available Nets     Pick Nets     Filter Nets with Wildcards     I) Traces Not Ready 3) Cutter No     2) Layers Ready 4) Co                                                                                                                                                                                                                                                                                                                                                             | Include all unnamed nets Reset TReady 5) Ports Not Ready pmponent/Pins Not Ready OK Cancel                                   |  |  |  |  |

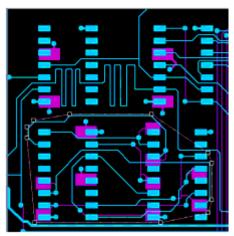

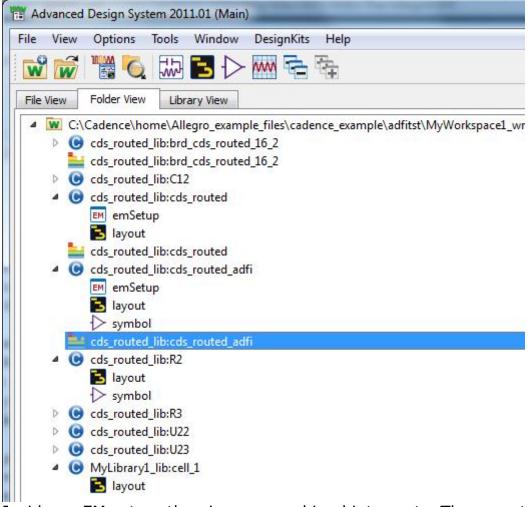

If you want to experiment now it is time to have a look at an example. Allegro ships with an simple example board cds\_routed.brd in the <Allegro install

directory>/share/pcb/examples/board\_design that you can easily experiment with. Copy this cds\_routed.brd file to a local directory and perform the Allegro uprev command if needed. Starting with this board you can follow the operations in the following sections in

the actual tool.

- Open cds\_routed.brd.

- Choose *Sample Fine Setting B* as export setup.

- Experiment with "CLK<i><+|->" signal nets, and "VCC"/"GND" RF ground nets.

- Upcoming sections provide tips when going through the various steps.

- Try to add a large net (PCLK) keeping the cookie cutter.

## Using the Trace Select Tab

The **Trace Select** tab enables you to add specific nets to the *Signal Nets* and *RF Ground Nets* output lists.

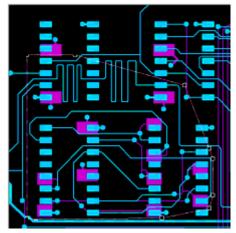

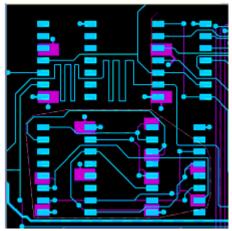

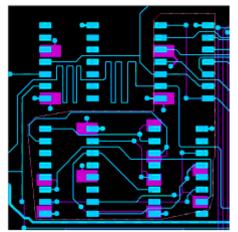

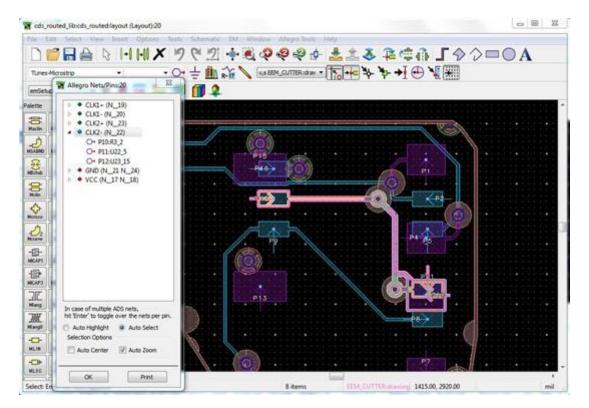

You can select nets for export can by choosing specific nets from the *Selectable Net Pool* and clicking the **Add** button in the *Signal Nets* section of the dialog, as shown below. The Nets selected in the list will appear as highlighted traces in the design.

You can populate **Selectable Net Pool** in the following ways:

- 1. By selecting **All Available Nets** located below the **Selectable Net Pool** window.

- 2. By picking specific nets from the Layout window.

To pick specific nets from the Layout window:

- 1. Select Pick Nets.

- 2. Increase zoom on the required area.

- 3. Click the specific net or nets you wish to add to the **Signal Nets** list.

The selected traces are highlighted in the design and appear in the *Selectable Net Pool*, as shown in the *Nets selected from the Layout window* (allegrolink).

#### Nets selected from the Layout window

Optionally, you can filter the selectable nets displayed in the selectable nets list by clicking the *Filter Nets with Wildcards* check-box and providing a filter pattern, as shown in *Selecting nets using a wildcard* (allegrolink). Pressing **Enter** on your *keyboard* implements your selection and populates the *Selectable Net Pool*.

| - Selectable Net Pool                                               |

|---------------------------------------------------------------------|

| CLK2<br>CLK1+<br>CLK2+<br>CLK2-<br>CLK3+<br>CLK3-<br>CLK4+<br>CLK4- |

| 💿 All Available Nets                                                |

| ○ Pick Nets                                                         |

| Filter Nets with Wildcards                                          |

| CLK*                                                                |

## Selecting nets using a wildcard

## **Selecting RF Ground Nets**

*RF Ground Nets* can be selected using the same steps required to select signal nets; selecting the nets from the list of all available nets, or by picking specific nets from the Layout window.

The **Include all unnamed nets** option allows you to select objects without an Allegro net name as RF Ground Net objects for exporting. When enabled the list of the RF Ground Nets in the select box will have an empty extra line at the top as indication of the extended net name filter used for all later processing. Individual selection of net objects without a name in Allegro is currently not possible because the ADFI tool has no reliable way to keep track of their selection state. If you want to use such objects in your Signal Nets, attach a name to the objects inside Allegro with **Logic > Net Logic**.

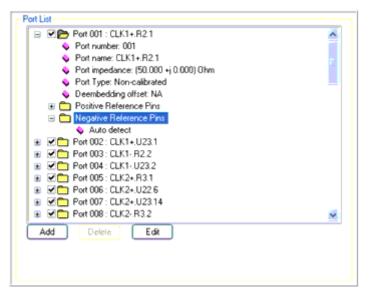

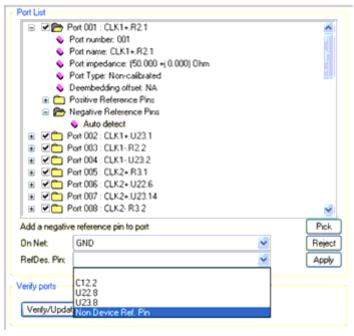

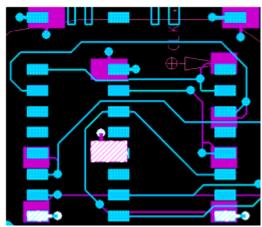

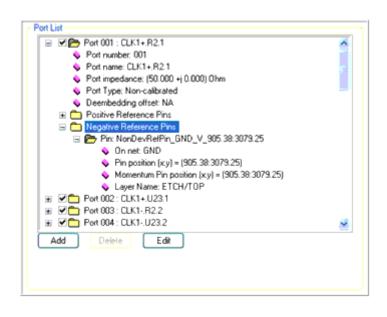

| Selectable Net Pool                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Signal Nets                                               |